為800V應用選擇合適的半導體技術

關鍵詞: 高壓中間母線轉(zhuǎn)換器 諧振轉(zhuǎn)換器拓撲 性能對比

面向AI數(shù)據(jù)中心高壓中間母線轉(zhuǎn)換器應用的橫向GaN HEMT、SiC MOSFET與SiC Cascode JFET的對比

摘要

隨著AI數(shù)據(jù)中心向更高功率密度和更高效能源分配演進,高壓中間母線轉(zhuǎn)換器(HV IBC)正逐漸成為下一代云計算供電架構(gòu)中的關鍵器件。本文針對橫向GaN HEMT、碳化硅MOSFET及SiC Cascode JFET(CJFET)三類寬禁帶功率器件,在近1 MHz高頻開關條件下用于高壓母線轉(zhuǎn)換器的性能展開對比分析。重點評估了導通損耗、開關特性、柵極電荷損耗及緩沖電路需求等關鍵指標。同時,本文亦探討了三種諧振轉(zhuǎn)換器拓撲——堆疊式LLC、單相LLC與三相LLC——對其系統(tǒng)效率與元件數(shù)量的影響。仿真結(jié)果表明,盡管三類半導體器件的系統(tǒng)總損耗相近,但CJFET因結(jié)構(gòu)簡單、驅(qū)動便捷,在成本方面具備顯著優(yōu)勢。在拓撲比較中,三相LLC通過有效降低RMS電流并減少元件數(shù)量,表現(xiàn)出更優(yōu)的綜合性能。本研究為未來高壓IBC設計中半導體選型與拓撲配置提供了理論依據(jù),安森美(onsemi)正開展相關實驗驗證工作。

引言

當前,云計算供電架構(gòu)正朝著更高傳輸電壓的方向演進。這一趨勢不僅體現(xiàn)在數(shù)據(jù)中心與電網(wǎng)的連接方式上——將通過固態(tài)變壓器直接接入中壓電網(wǎng),也體現(xiàn)在數(shù)據(jù)中心內(nèi)部的電力分配系統(tǒng)中——其正逐步轉(zhuǎn)向高壓直流配電架構(gòu)。在該架構(gòu)下,計算托盤將直接連接至800V直流母線,隨后通過高壓IBC將電壓降至50V或12V,為下游負載供電。

高壓IBC具備以下關鍵特性:

實現(xiàn)電壓降壓(16:1或64:1變換比)

提供電氣隔離以保障安全

非穩(wěn)壓輸出

具備短時過載能力

超緊湊的外形尺寸

轉(zhuǎn)換效率高

本白皮書將重點圍繞實現(xiàn)上述目標的轉(zhuǎn)換器拓撲結(jié)構(gòu)與半導體技術展開探討。內(nèi)容主要聚焦于原邊的拓撲選擇與半導體器件;副邊假定采用低壓硅基MOSFET,并配置為中心抽頭電流倍增器或全橋結(jié)構(gòu)。

半導體技術

為滿足高壓IBC在小型化設計中無源元件的布局要求,系統(tǒng)需以極高的開關頻率(接近1 MHz)運行。因此可選的半導體器件被限定為寬禁帶器件,主要包括:氮化鎵高電子遷移率晶體管(GaN HEMT)、碳化硅金屬氧化物半導體場效應晶體管(SiC MOSFET)以及SiC Cascode JFET(CJFET)。在本應用中,上述器件的關鍵評估指標集中于導通損耗、開關特性與成本三個方面。

導通損耗

這三種器件在導通狀態(tài)下均可用電阻Rds,on來表征(與IGBT等具有恒定導通壓降的器件不同)。因此,其導通損耗與流經(jīng)電流的平方成正比:

Pcon=Rds,on × I2ds

(方程1)

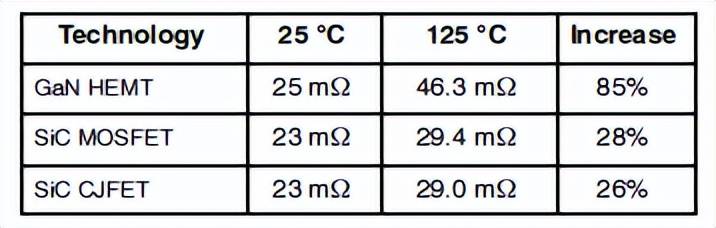

Rds,on會隨溫度升高而增加,其標稱值僅適用于25℃的結(jié)溫。下表對比了典型GaN器件、安森美(onsemi)M3S 650 V器件以及安森美第四代CJFET 750 V器件的導通電阻隨溫度上升的情況。

表1. 不同結(jié)溫下的Rds,on值

在為特定應用確定正確的Rds,on值時,必須考慮這種增加。

開關特性

在“轉(zhuǎn)換器拓撲”一節(jié)中探討的所有拓撲結(jié)構(gòu)均受益于軟開關特性,其固定電流可在轉(zhuǎn)換器設計階段進行優(yōu)化。在開關轉(zhuǎn)換瞬間,諧振電流為零,僅勵磁電流流通,而該電流可通過調(diào)整變壓器勵磁電感(例如改變氣隙)等參數(shù)靈活控制。因此,三種半導體技術在開關過程中產(chǎn)生的損耗可忽略不計。然而,其寄生電容仍顯著影響開關軌跡。

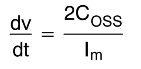

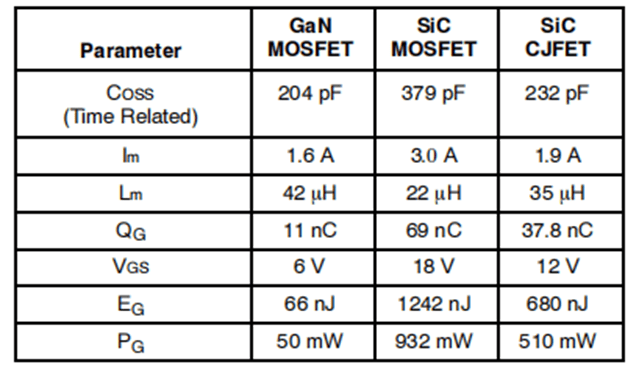

影響開關特性的主要差異源于器件的輸出電容(COSS)。通常,SiC MOSFET具有較大的COSS,這是由于其需要更大的裸芯尺寸才能實現(xiàn)與GaN HEMT或SiC CJFET相當?shù)膶娮瑁≧ds,on),如表2所示。該電容與勵磁電流共同決定了半導體器件的開關轉(zhuǎn)換速度。

(方程2)

在此過渡階段,轉(zhuǎn)換器不傳輸任何功率。因此,將其保持在整個開關周期的較小比例更為有利。對方程(2)進行時間變量積分并求解勵磁電流,可得到方程(3)。

(方程 3)

該方程可用于計算在給定時間(td)內(nèi),根據(jù)半導體器件的電容(COSS)完成電壓轉(zhuǎn)換所需的勵磁電流(Im)。表2列出了各半導體技術對應的結(jié)果。

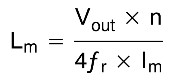

達到該勵磁電流所需的勵磁電感,可通過以下方式推導:對施加在變壓器原邊的電壓(該電壓由副邊反射而來)進行積分,再除以所需的勵磁電流,如方程(4)所示。

(方程 4)

其中Vout為輸出電壓,n為變壓器變比,?r為開關(諧振)頻率。表2列出了三種半導體技術對應的勵磁電感值。

其次,在計算損耗時,還需考慮驅(qū)動半導體器件導通所需的柵極電荷所引起的輔助損耗。該電荷值通常在器件數(shù)據(jù)手冊中給出,將所需柵極電荷乘以柵源電壓VGS,即可得到存儲在柵極上的能量。該能量在器件每個開關周期關斷時耗散一次。存儲能量乘以開關頻率即為因放電導致的功率損耗(PG)。此外,柵極電容充電過程中還存在柵極驅(qū)動器和電阻產(chǎn)生的額外損耗,本文暫不討論。表2給出了三種半導體配置對應的上述損耗值:SiC MOSFET因柵極導通電壓高、柵極電荷大,其柵極損耗顯著;相比之下,CJFET的柵極損耗約為SiC MOSFET的一半,這得益于其較低的柵極驅(qū)動電壓以及由低壓MOSFET(由驅(qū)動器直接驅(qū)動)所帶來的較小柵極電荷;而GaN器件表現(xiàn)最優(yōu),其柵極電荷損耗比前兩者小10~20倍。

表2. 一個25mΩ器件,在以下條件下運行的參數(shù)對比:?r=750 kHz,Vout=12.5 V,n=16,Vdc=400 V,td=100 ns)

緩沖電路(Snubber)

在快速開關過程中,CJFET可能因寄生電感、電容與快速電壓變化的相互作用而產(chǎn)生振鈴現(xiàn)象。盡管該拓撲有助于抑制米勒效應并提升帶寬,但同時會引入易引發(fā)諧振的高阻抗節(jié)點。因此,精心優(yōu)化的PCB布局與有效的抑制措施對于控制此類振鈴尤為關鍵,常見方法是在晶體管兩端并聯(lián)緩沖電路。

然而,此類振鈴現(xiàn)象主要源于CJFET在硬開關過程中半導體器件間的快速切換。當CJFET用于軟開關應用時,該問題可得到顯著緩解。圖1展示了CJFET在500kHz LLC諧振轉(zhuǎn)換器中運行時的實測結(jié)果。

圖1. CJFET在LLC諧振轉(zhuǎn)換器中工作時的漏源電壓實測波形

測量在LLC運行開始時進行。由于運行初始階段勵磁電感未充電,首次換流是硬開關方式。因此,在未并聯(lián)緩沖電路的情況下,CJFET的漏源極電壓會產(chǎn)生振鈴現(xiàn)象。然而,僅經(jīng)過兩個開關周期后,勵磁電流便已足夠大,能夠?qū)崿F(xiàn)開關的換流。此后,無論是否使用緩沖電路,實測波形幾乎無明顯差異。

對于CJFET而言,無需額外配置緩沖電路具有顯著優(yōu)勢:不僅節(jié)省了PCB面積和物料成本,又能消除轉(zhuǎn)換器設計中的一個損耗來源。

損耗

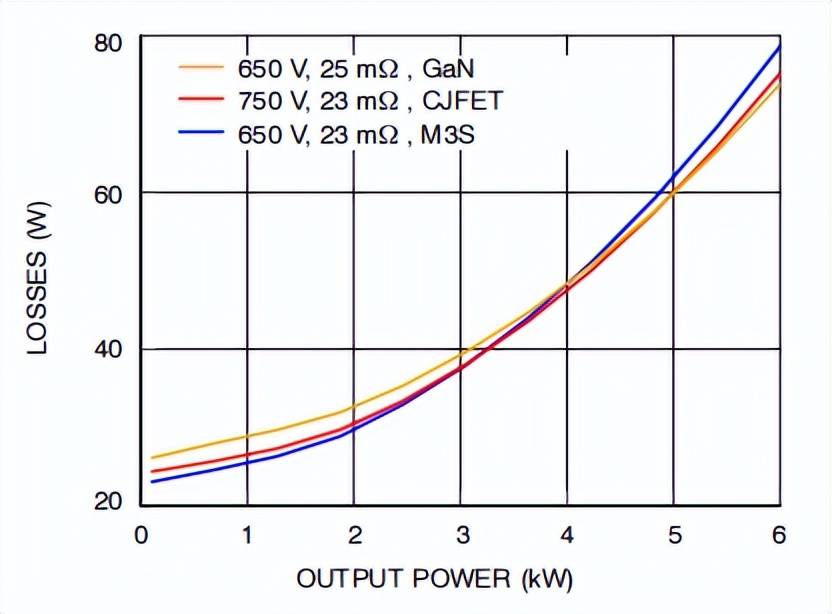

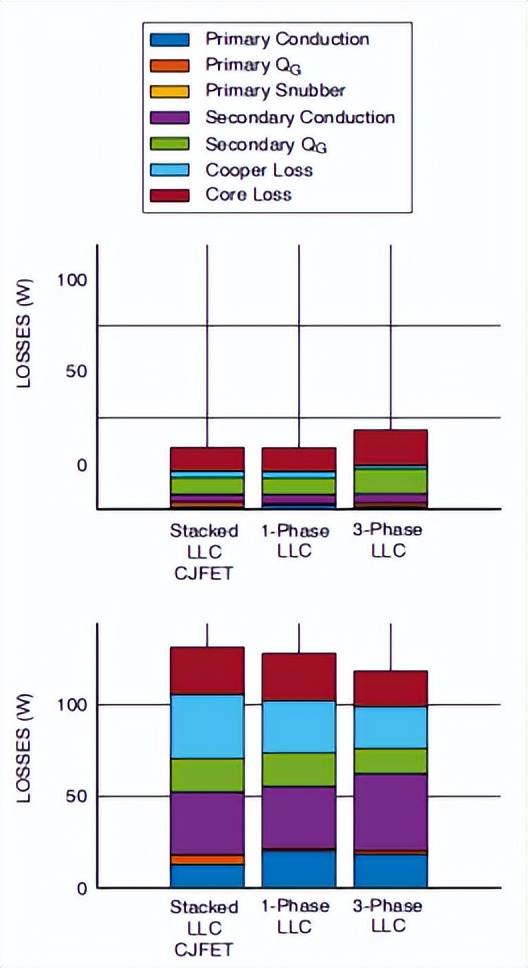

為基于損耗對比三種半導體器件的性能,需進行系統(tǒng)級仿真。例如,更大的輸出電容(COSS)需更大的勵磁電流,從而增加變壓器銅損。圖2展示了堆疊式LLC轉(zhuǎn)換器的總損耗,包括磁芯損耗、銅損、柵極驅(qū)動損耗以及開關與導通損耗,其中所仿真的轉(zhuǎn)換器與“轉(zhuǎn)換器拓撲”一節(jié)中所述的規(guī)格和設計相匹配。

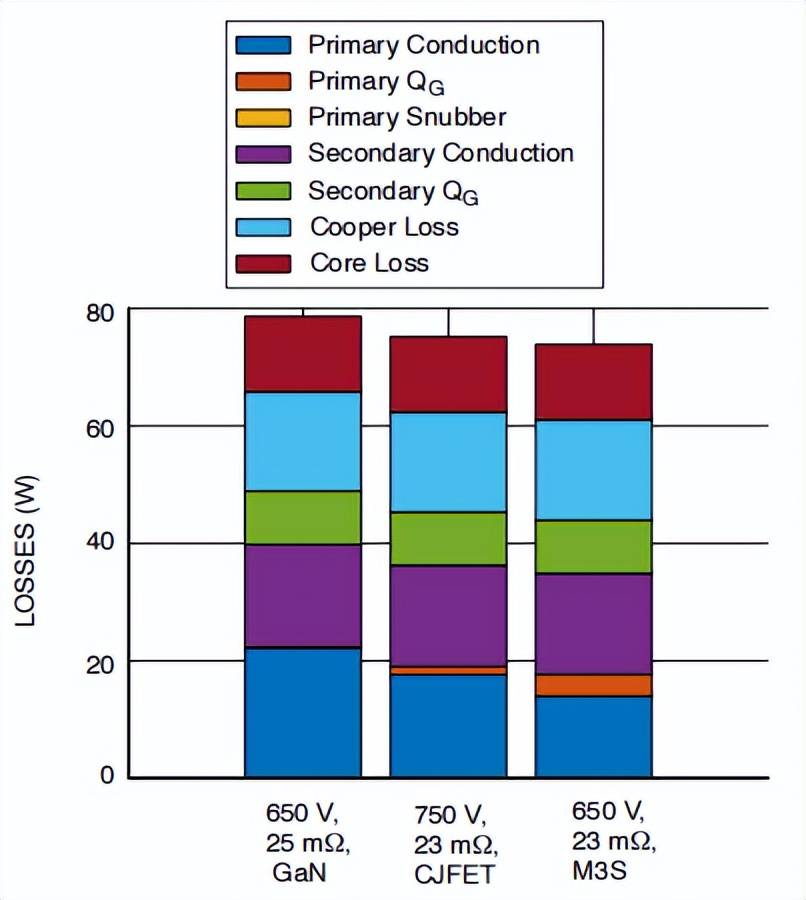

三種器件的總損耗對比結(jié)果顯示其性能幾乎相同。為深入分析,圖3進一步給出了按損耗來源分解的結(jié)果。該分解表明,在此轉(zhuǎn)換器中,半導體技術的選擇對整體損耗影響甚微:GaN HEMT雖柵極驅(qū)動損耗較低,但其較高的導通電阻導致導通損耗增加,最終使各類器件的整體表現(xiàn)趨于一致。

圖2. 采用不同原邊開關器件的堆疊式LLC轉(zhuǎn)換器系統(tǒng)損耗

圖3. 采用不同原邊開關器件的堆疊式LLC轉(zhuǎn)換器在標稱功率下的系統(tǒng)損耗來源分解

各損耗來源顏色標識如下:磁芯損耗:暗紅色;PCB繞組銅損:淺藍色;副邊柵極電荷損耗:綠色;副邊導通損耗:紫色;原邊柵極電荷損耗:橙色;原邊導通損耗:深藍色

轉(zhuǎn)換器拓撲

諧振式轉(zhuǎn)換器拓撲具有超高的功率密度,但代價是在寬輸入或輸出電壓范圍內(nèi)效率降低。由于高壓IBC具有固定的輸入輸出電壓比以及對超高功率密度的需求,因此諧振拓撲非常適合此類應用。

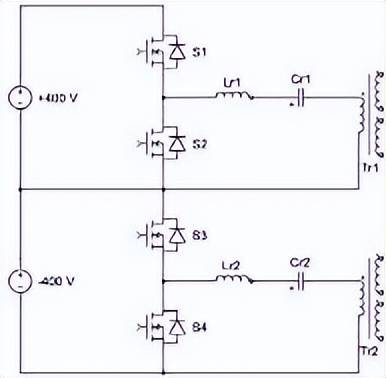

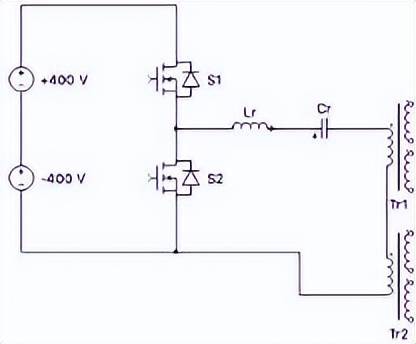

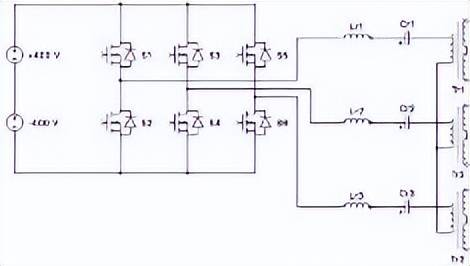

諧振拓撲存在多種方案,本研究將對其中的三種進行探討,如圖4所示。圖4a展示了一種堆疊式LLC轉(zhuǎn)換器(sC),其主要優(yōu)勢在于可采用650V級別的開關器件實現(xiàn)高壓IBC。圖4b所示為單相LLC轉(zhuǎn)換器(1pC),其原邊使用的器件數(shù)量最少。圖4c展示了一種三相LLC轉(zhuǎn)換器(3pC),它得益于三相拓撲固有的更低RMS電流和電壓紋波,可縮小元器件的尺寸。

sC的原邊

1pC的原邊

3pC的原邊

圖4. 本研究中探討的三種轉(zhuǎn)換器拓撲原邊電路

系統(tǒng)規(guī)格

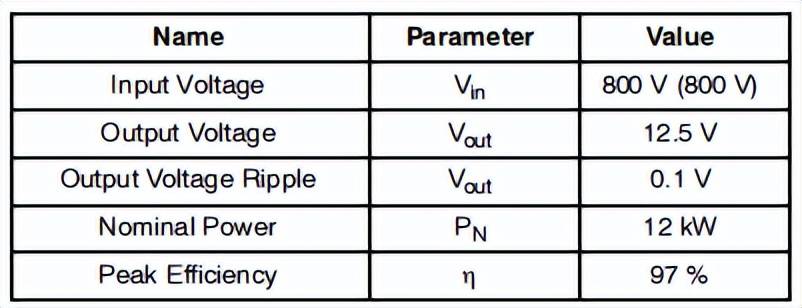

本研究基于仿真結(jié)果對三種拓撲結(jié)構(gòu)及半導體技術進行對比分析。仿真采用PLECS軟件平臺,基于安森美針對CJFET和SiC MOSFET的Elite Power仿真工具,以及通用橫向GaN模型。表3列出了本次仿真所用的高壓IBC規(guī)格參數(shù)。

表3. 本次分析中使用的高壓IBC規(guī)格參數(shù)

采用sC和1pC的高壓IBC系統(tǒng)將拆分為兩個轉(zhuǎn)換器,各承擔一半標稱功率(每臺6kW)。此舉旨在將原邊RMS電流降至可控水平(詳見下面轉(zhuǎn)換器物料清單章節(jié))。3pC方案將通過一臺12kW轉(zhuǎn)換器實現(xiàn)。

轉(zhuǎn)換器損耗

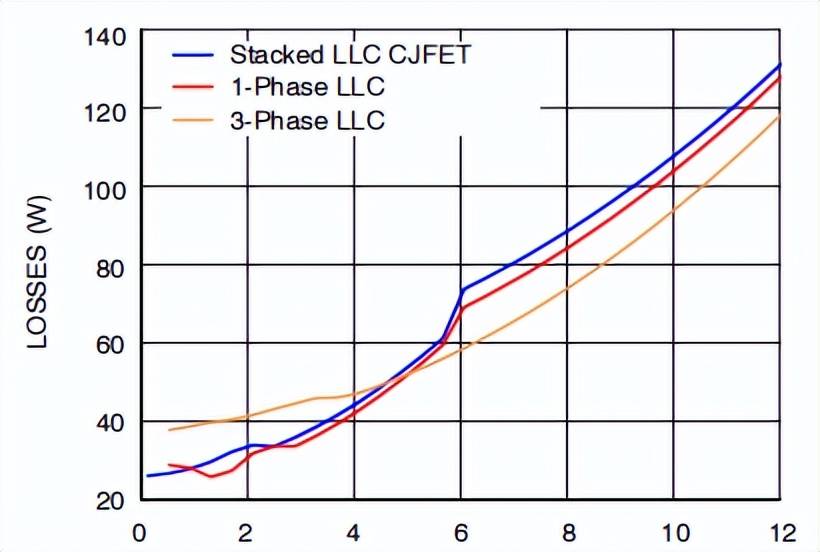

三種拓撲結(jié)構(gòu)的損耗如圖5所示。

輸出功率(kW)

圖5. 采用不同原邊開關器件的sC系統(tǒng)損耗

sC與1pC的損耗特性較為相似。兩者均在約50%標稱功率處出現(xiàn)損耗的躍升。這是因為在該功率點,構(gòu)成12 kW系統(tǒng)的兩個變換器單元中的第二個轉(zhuǎn)換單元投入運行,導致磁芯損耗和柵極電荷輔助損耗翻倍。而3pC的損耗隨功率增加上升較為平緩,這得益于三相拓撲本身所具有的更低RMS電流特性。然而,在低功率條件下,由于所有變壓器和副邊開關器件持續(xù)運行,其損耗相較于sC和1pC更高。這一特性亦可從圖6所示的損耗細分中得到印證。

圖6. 研究的三種拓撲結(jié)構(gòu)系統(tǒng)損耗分解。上圖顯示3 kW時的損耗,下圖顯示12 kW時的損耗。

各損耗來源顏色標識如下:磁芯損耗:暗紅色;PCB繞組銅損:淺藍色;副邊柵極電荷損耗:綠色;副邊導通損耗:紫色;原邊柵極電荷損耗:橙色;原邊導通損耗:深藍色

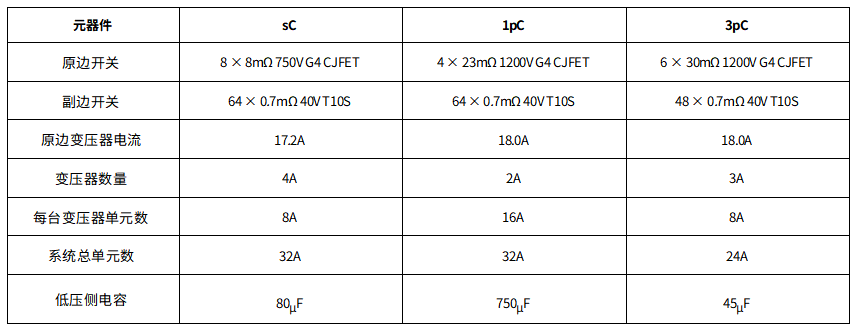

表4. 12kW轉(zhuǎn)換器系統(tǒng)物料清單

轉(zhuǎn)換器物料清單(BOM)

采用前述三種拓撲結(jié)構(gòu)的12 kW轉(zhuǎn)換器系統(tǒng)的物料清單如表4所示。

盡管1pC所需的原邊器件數(shù)量最少,但整體器件總數(shù)最少的方案卻是3pC。這得益于三相拓撲固有的較低RMS電流特性,不僅減少了副邊器件數(shù)量,也簡化了變壓器設計。

sC每個轉(zhuǎn)換單元使用兩個矩陣式變壓器,整個12 kW系統(tǒng)共需四個變壓器。每個變壓器包含八個基本變壓器單元,總計達32個單元。而1pC的配置則不同:每個轉(zhuǎn)換器僅需一個變壓器,但由于其所需變壓比高于sC,該變壓器的單元數(shù)量需翻倍。

而3pC僅需三個變壓器,每個包含八個基本單元,是三種方案中基本變壓器單元數(shù)量最少的。

此外,在輸出電容需求方面,3pC也具有明顯優(yōu)勢。相比之下,1pC所需的電容尺寸過大,幾乎無法滿足合理設計的要求。

結(jié)語

本研究探討的三種半導體技術(GaN HEMT、SiC MOSFET、SiC CJFET)在高壓IBC應用中表現(xiàn)幾乎一致。由于諧振拓撲的軟開關特性,它們的開關損耗差異影響甚微。通過合理選擇勵磁電感,可規(guī)避其寄生電容差異帶來的影響。最后,各技術間的損耗差異微乎其微,因此成本將成為關鍵決策因素。CJFET憑借簡化的器件結(jié)構(gòu)實現(xiàn)高效制造工藝,在成本效益方面顯著優(yōu)于其他技術。

相較于sC和1pC,3pC憑借其更低的RMS電流具有顯著優(yōu)勢,減少了物料清單中的元件數(shù)量(特別是副邊開關器件和變壓器組件)。這些優(yōu)勢可在轉(zhuǎn)換器設計中靈活利用——既可用于提升功率密度,也可通過增大單個器件尺寸(例如采用更大的變壓器磁芯以降低峰值磁通密度,從而減少磁芯損耗)來進一步優(yōu)化性能。

上述仿真結(jié)果將通過安森美正在開發(fā)的高壓IBC硬件實測數(shù)據(jù)進行驗證。