數模轉換器(DAC/ADC)信號轉換的原理

關鍵詞: 數模轉換器 DAC 加權電阻DAC R-2R梯形DAC 信號轉換 分辨率

數模轉換器(DAC/ADC)信號轉換的原理

數模轉換器 (DAC) 利用每個比特的加權貢獻將數字二進制數據轉換為模擬信號。在本常見問題解答中,我們討論了兩種最常見的 DAC 轉換方式:加權電阻 DAC 和 R-2R 梯形 DAC。

在進入轉換類型之前,讓我們了解 DAC 轉換所涉及的基本步驟。

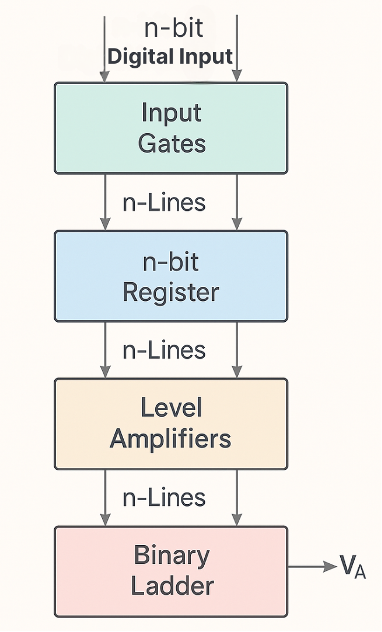

圖 1 顯示了 DAC 中發生的過程的模塊示意圖。系統通過幾個階段處理 n 位數字輸入:

首先,輸入門接收數字信號

其次,n 位寄存器存儲這些值

第三,電平放大器調節信號

第四,二進制梯形圖將這些加權信號組合在一起,以產生模擬輸出電壓 (VA)。

圖 1.包含各個轉換階段的 DAC 架構框圖。

N 行連接每個階段,在整個轉換過程中保持 n 位分辨率。

加權電阻 DAC

加權電阻 DAC 是一種 DAC,它使用的電阻值與輸入位的權重成正比。它根據輸入的表示對電流或電壓求和,將數字輸入信號轉換為等效的模擬輸出信號。

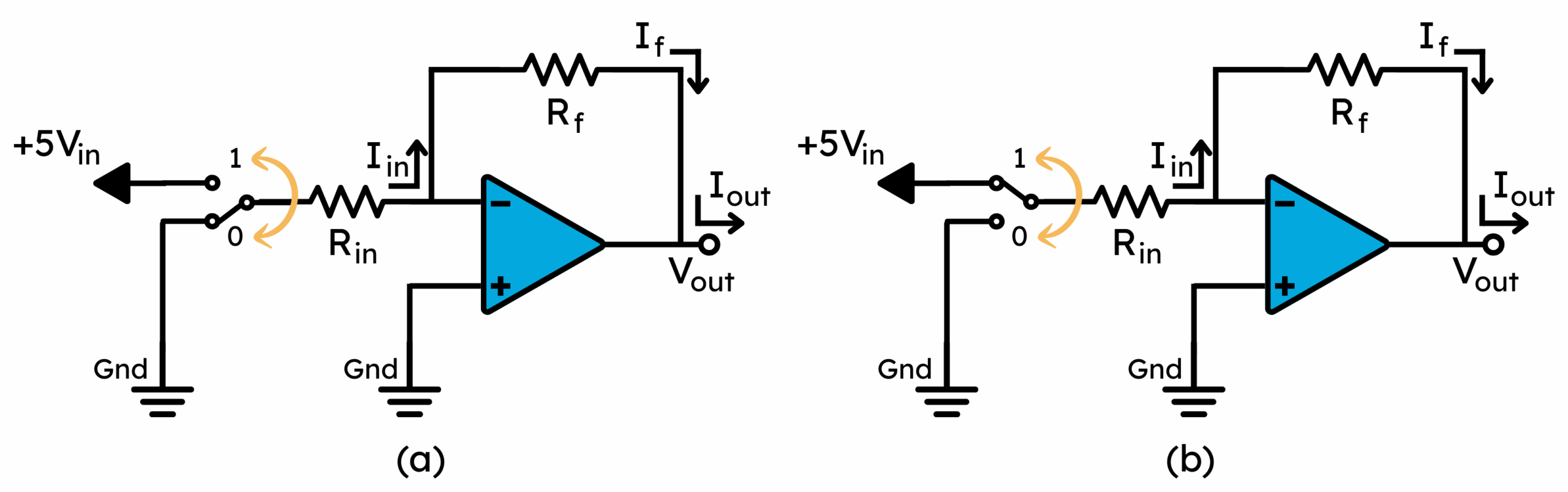

從圖 2 開始,可以理解加權電阻 DAC 的簡單版本。該圖說明了基本 DAC 的兩種相同配置 (a) 和 (b),在反相模式下使用運算放大器。

圖 2.使用運算放大器的簡單 1 位 DAC。

每個設置都顯示一個通過開關連接到 +5 V 或接地的單位輸入(邏輯 '1' 或 '0'),通過電阻器 Rin 將電流饋入運算放大器的反相端子。同相端子接地。

一個反饋電阻器 Rf 將輸出 Vout 連接回反相輸入,確保負反饋和線性作。電流 Iin 通過 Rin 產生一個成比例的輸出電壓 Vout,通過 Rf 產生一個代表數字輸入狀態的模擬電壓。這種配置是加權電阻 DAC 的基本構建模塊。

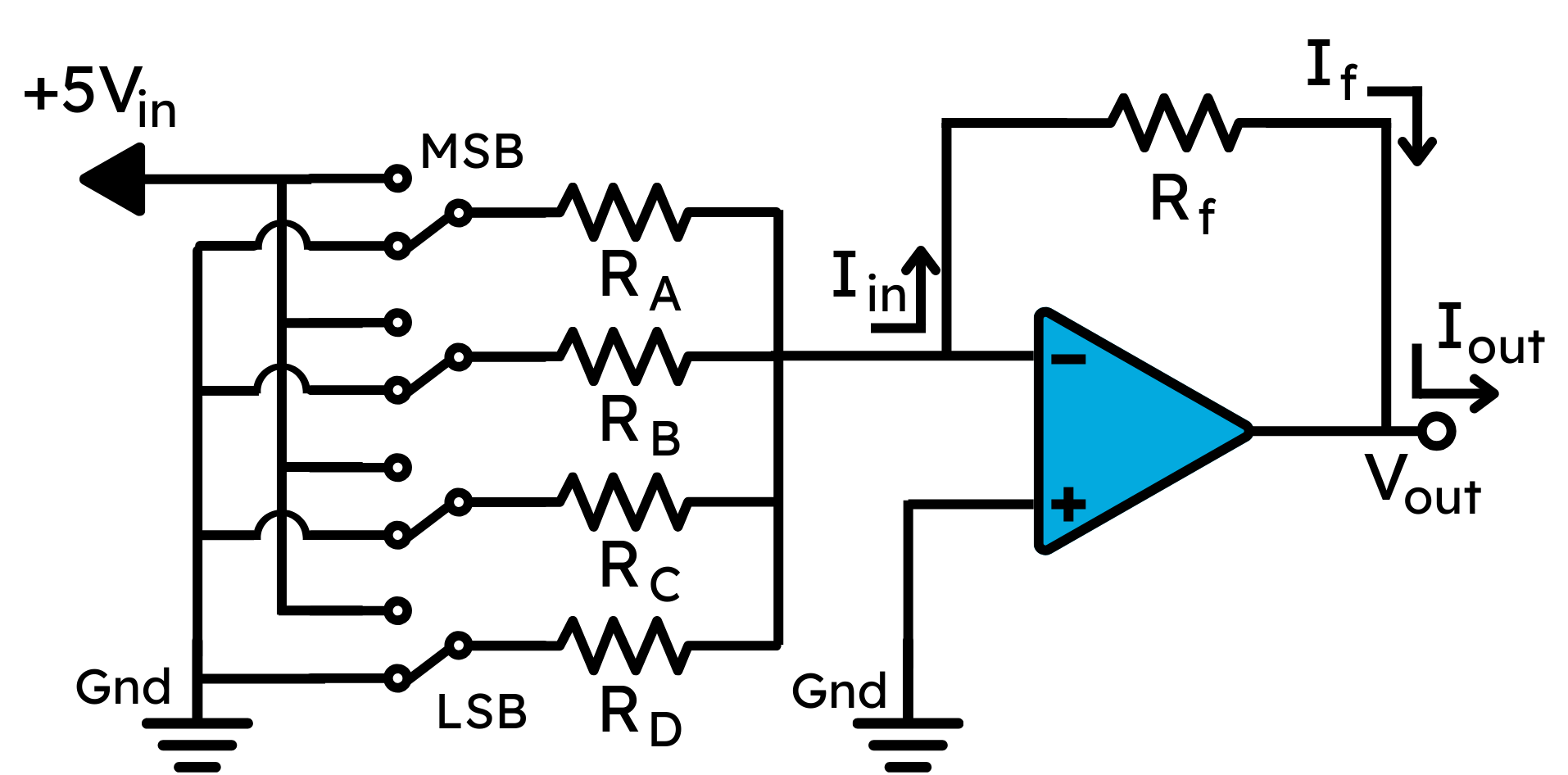

圖 3.4 位加權電阻 DAC 的一般原理圖。

圖 3 顯示了使用反相運算放大器配置的 4 位加權電阻 DAC。四個數字輸入位中的每一個都連接到一個開關。輸入從最低有效位 (LSB) 到最高有效位 (MSB) 排列。這些輸入通過單獨的電阻 RA、RB、RC 和 RD,這些電阻根據每個位的意義進行加權。

加權電流在運算放大器的反相輸入端組合,產生總輸入電流 Iin。電流通過反饋電阻器,反饋電阻器被轉換為成比例的電壓輸出 Vout。該電路對數字輸入位進行加權和,并提供與數字輸入值對應的模擬電壓輸出。

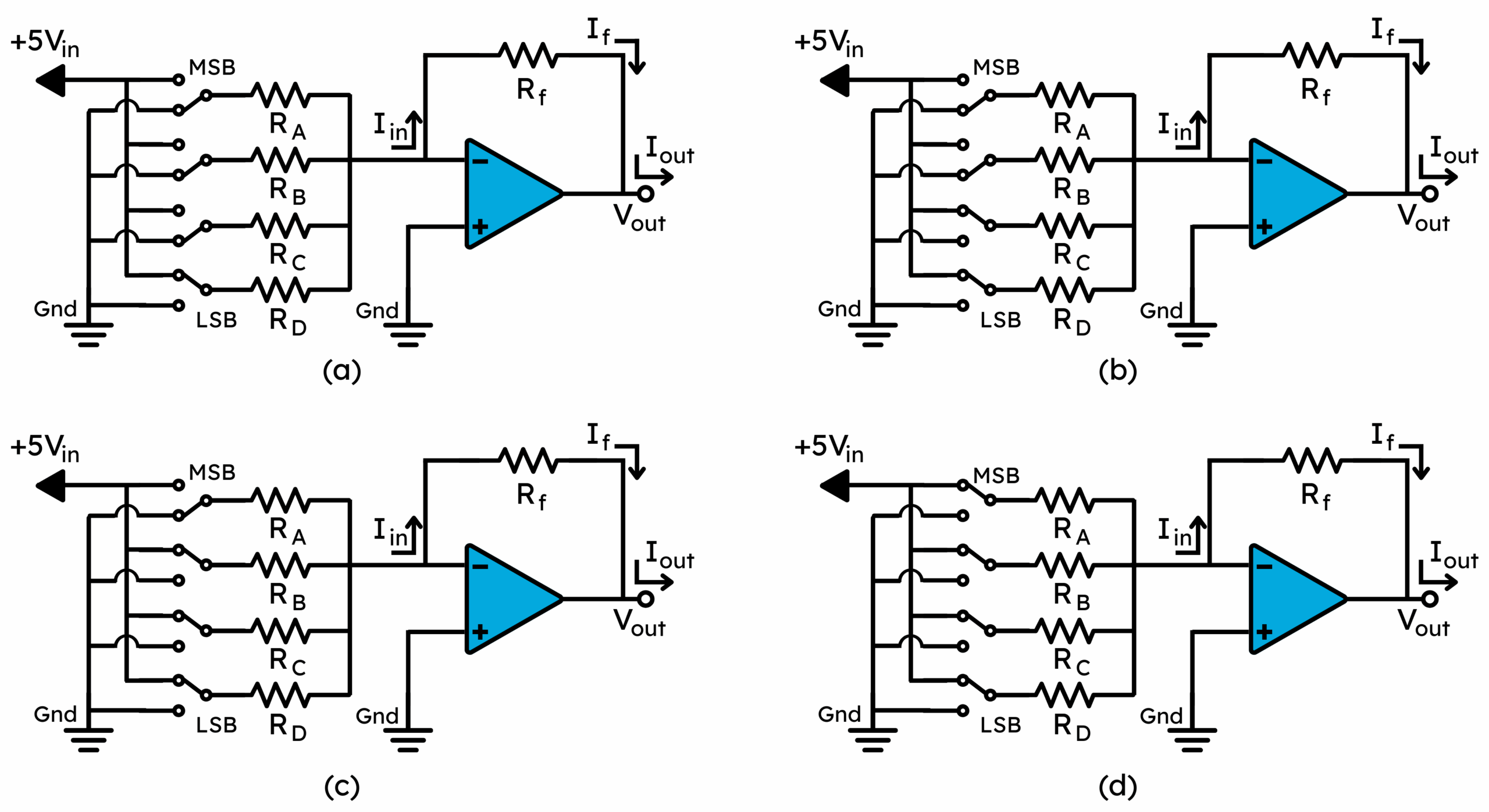

圖 4 顯示了 4 位加權電阻 DAC 的逐步作,如四個子圖 (a) 至 (d) 所示。每個子圖表示應用于連接到參考電壓 (+5 V) 和接地的一系列開關的不同輸入組合。

圖 4.4 位加權電阻 DAC 的各種工作模式,從 0001 到 1111。

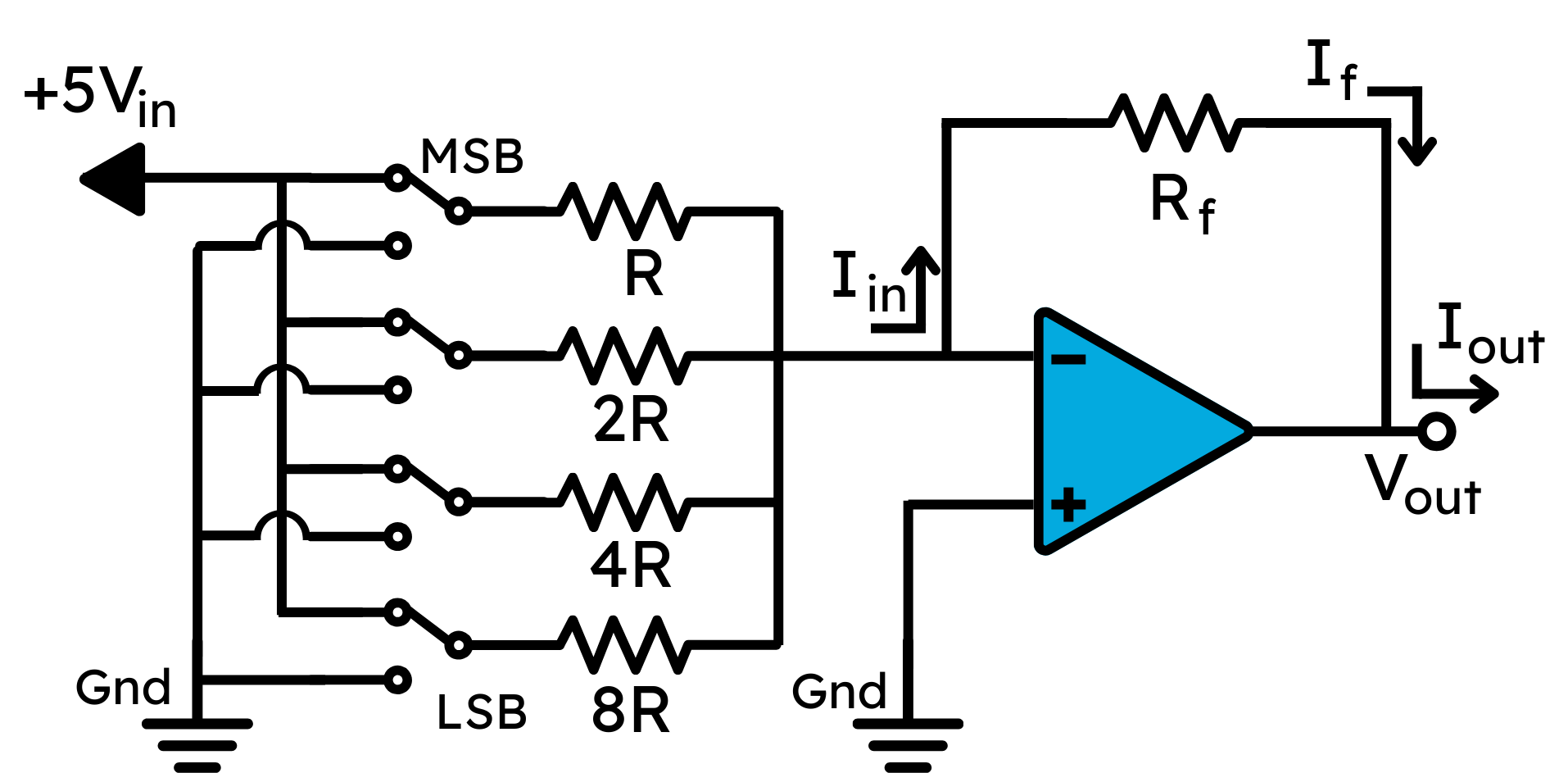

DAC 的實際應用是電阻器以二進制方式排列,如圖 5 所示。每個開關輸出都通過一個電阻器饋送,該電阻器具有二進制加權電阻值:R、2R、4R 和 8R,對應于該位的意義。這種方法的優點是總共可以實現 16 個狀態,從而提高了 DAC 的分辨率。

圖 5.4 位二進制加權電阻 DAC,提供比具有相同電阻值的 DAC 更好的分辨率。

R-2R 梯形 DAC

二進制加權電阻 DAC 的問題是需要很寬的電阻值范圍。例如,一個 12 位二進制加權 DAC 需要 1 kΩ (MSB) 到 2 MΩ (LSB) 的電阻,這使得制造具有挑戰性。增加挑戰的是電阻器需要高容差值才能獲得更高的精度。

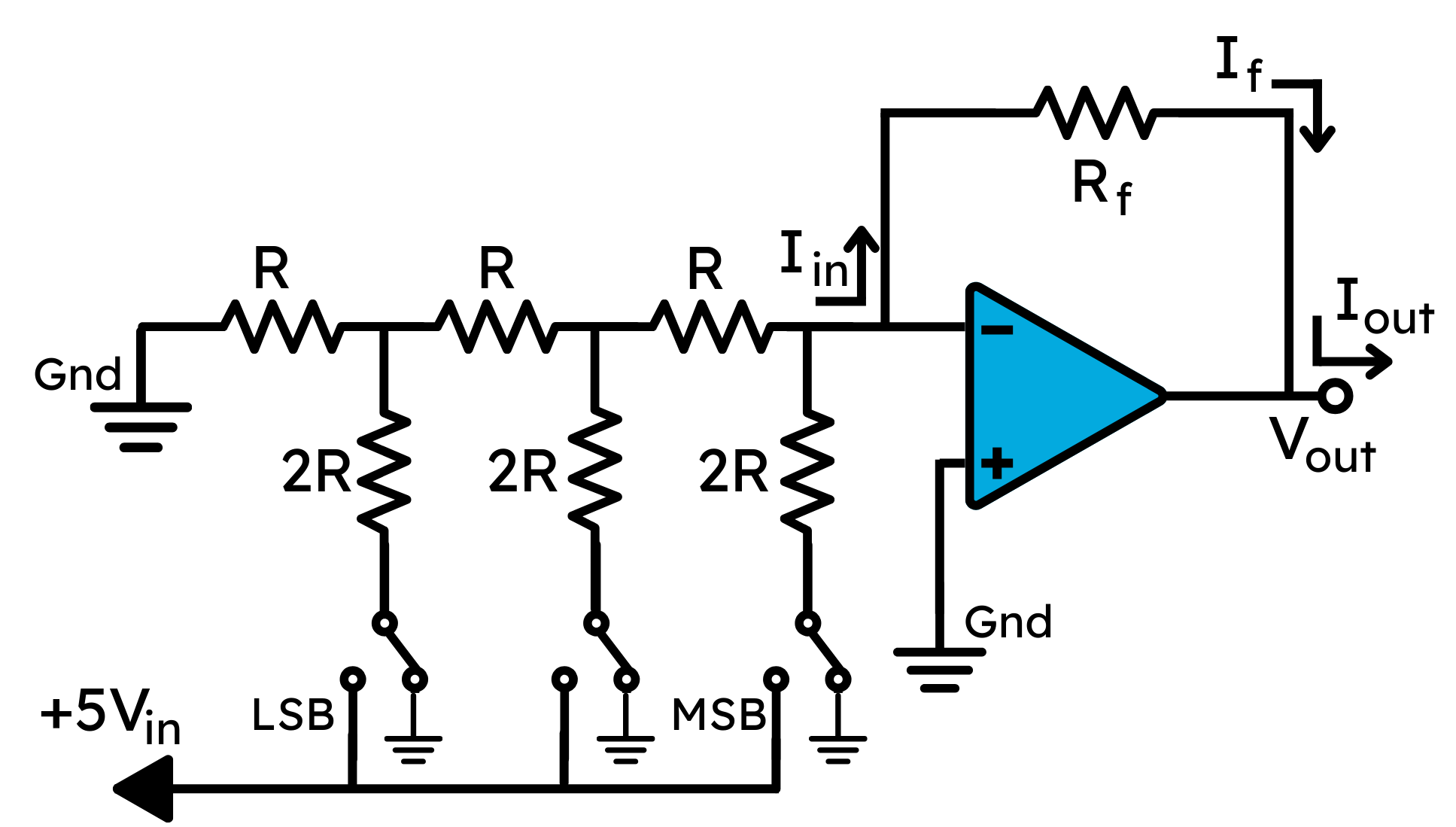

這些問題可以通過 R-2R 梯形 DAC 來解決,如圖 6 所示。 它說明了使用反相運算放大器配置實現的 3 位 R-2R 梯形 DAC。梯形網絡由值為 R 和 2R 的重復電阻段組成,它們形成一個分壓器,精確稱量每個數字輸入位(從 MSB 到 LSB)。

圖 6.3 位 R-2R 梯形 DAC 的電路圖。

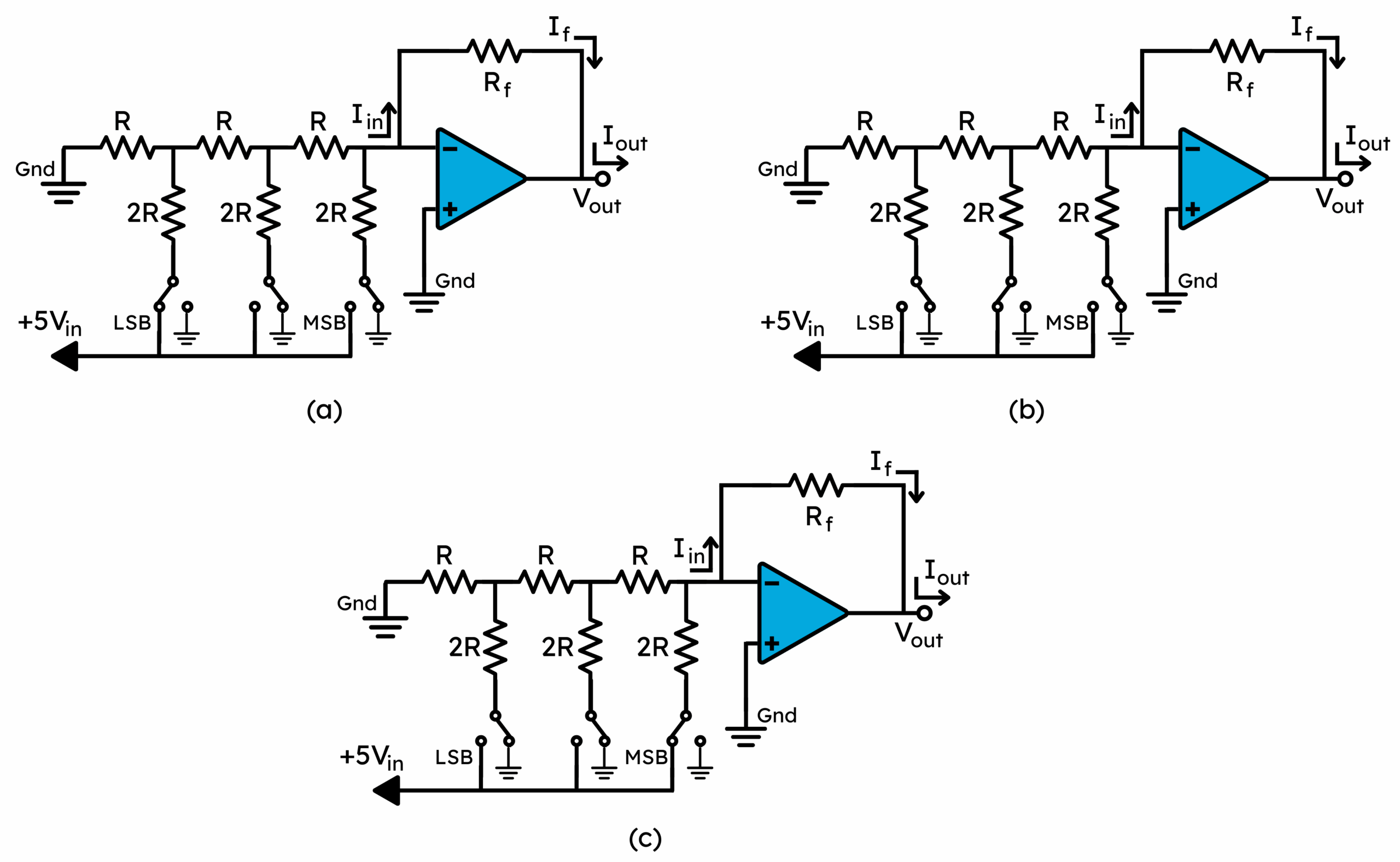

圖 7 顯示了 3 位 R-2R 梯形 DAC 在子圖 (a)、(b) 和 (c) 中的三種不同數字輸入組合上的作。每個配置都包括一個值為 R 和 2R 的電阻器網絡,以梯形結構連接。這些配置可實現八種不同的狀態,從而提高分辨率。

圖 7.3位R-2R梯形DAC的八種可能狀態中的三種。

R-2R 梯形圖的優勢在于,它可以擴展到更多位,而不受二進制加權電阻 DAC 中的電阻值挑戰。

總結

加權電阻 DAC 對電阻的二進制組合有效。由于簡單性,它們通常用于需要低分辨率數模轉換的應用,例如音頻設備、調光器和數字面板儀表。

R-2R 梯形 DAC 的實現更簡單,只有兩個電阻值。這一優勢使它們成為經濟高效且精確的通信系統和儀器儀表設計的理想選擇,例如波形生成和數據采集系統。

網址:www.baitaishengshi.com